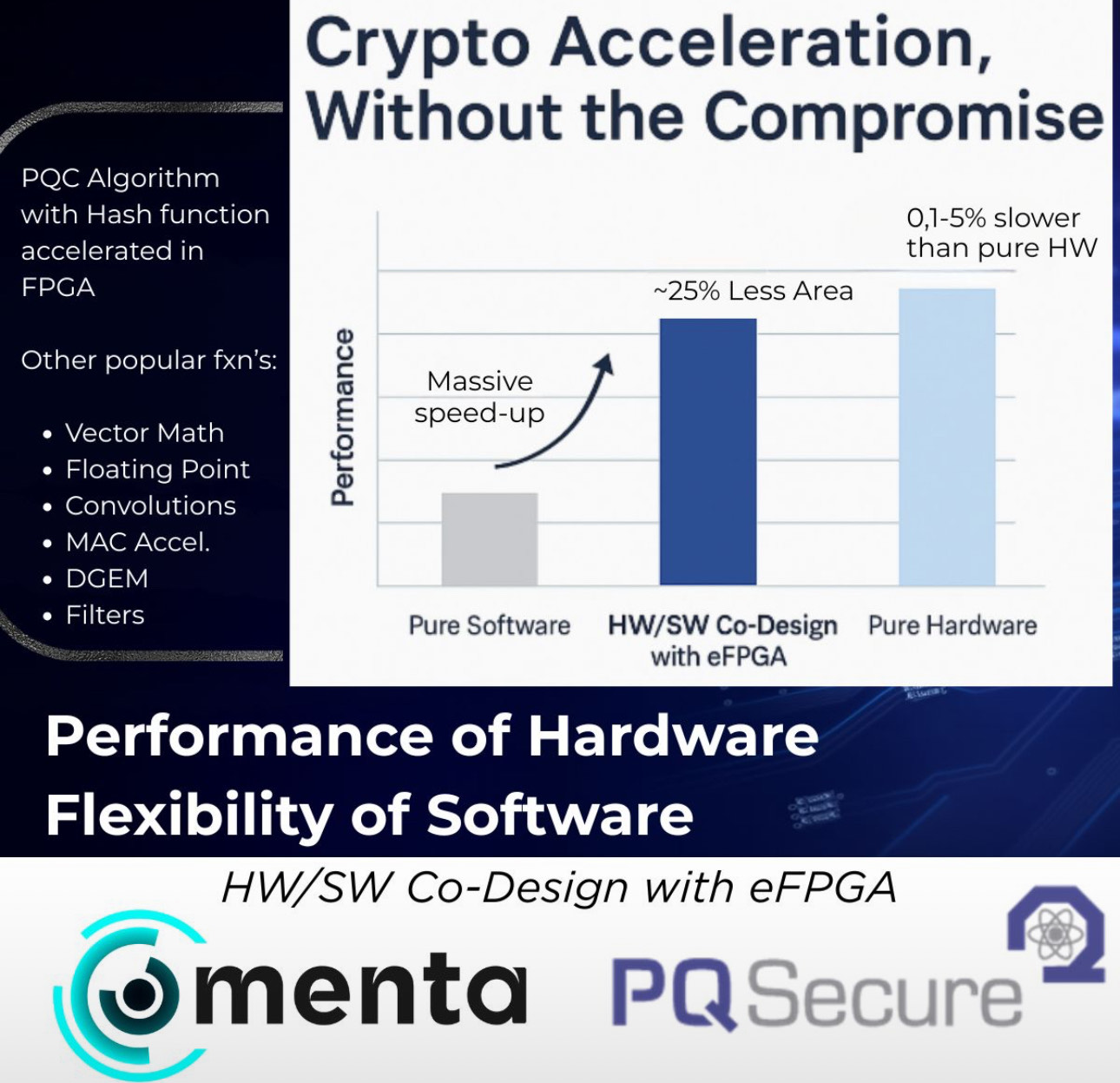

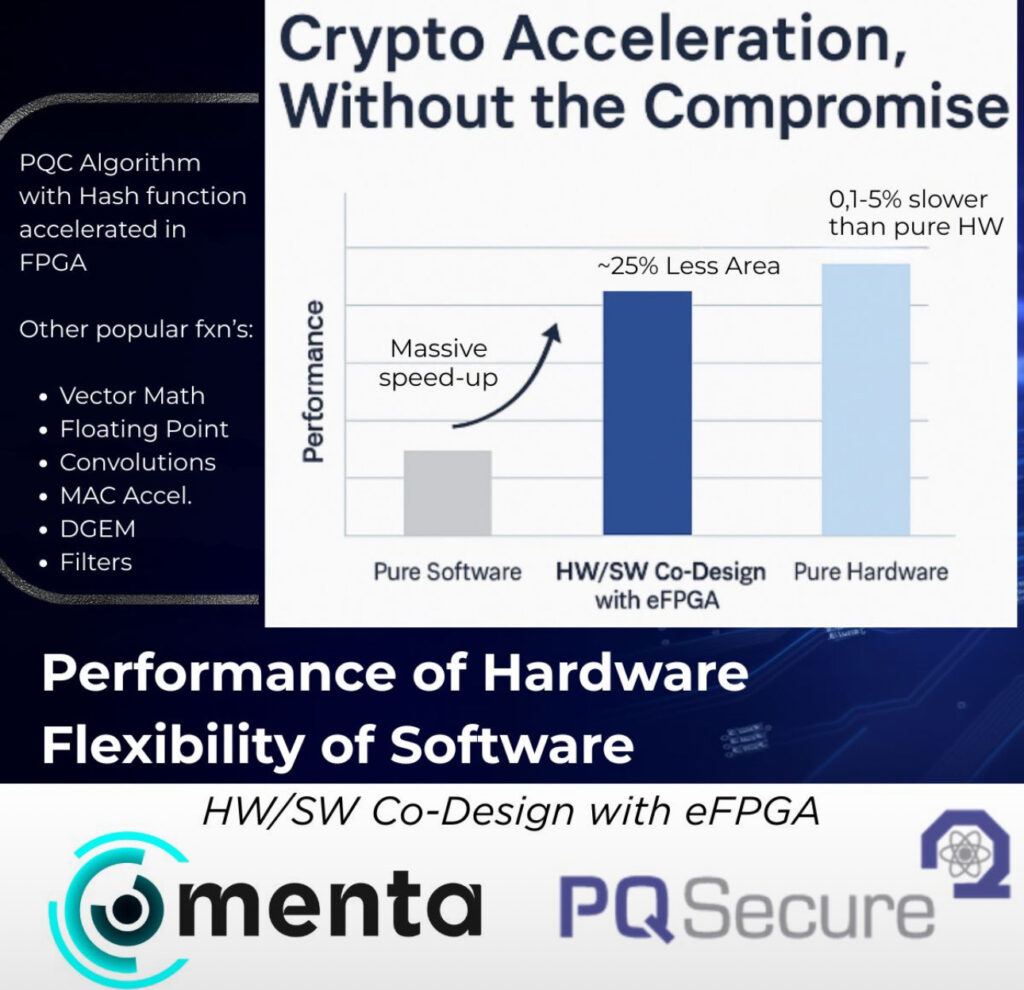

In collaboration with Menta, PQSecure has demonstrated how hardware/software co-design with eFPGA can deliver both performance and flexibility for post-quantum cryptography.

By partitioning the XMSS algorithm, our approach lets processor manage dataflow and memory, while the eFPGA accelerates computationally heavy lattice-based operations. The result:

- Performance comparable to full hardware implementation

- Approximately 25% reduction in eFPGA die area

- Software-level control, ideal for development teams

This design flow, which is supported by tools like Siemens Catapult, Codasip, and AndesTech CoPilot, makes crypto agility practical without compromising efficiency or adaptability.