PQSecure-HW/SW Co-Design™

Secure, Agile, and Upgradeable Post-Quantum Architectures

PQSecure-HW/SW Co-Design™ delivers tightly integrated hardware and software cryptographic architectures engineered for secure lifecycle management and long-term post-quantum migration. Unlike standalone accelerators or pure software stacks, PQSecure™ provides unified system-level security built around performance, flexibility, and upgradeability.

Crypto Agility Built Into Silicon

Crypto Agility is the ability to upgrade, replace, or hybridize cryptographic algorithms without redesigning hardware.

- Runtime-selectable algorithms

- Hybrid Classical + PQC operation

- Firmware-controlled cryptographic dispatch

- Modular accelerator interfaces

- Forward compatibility for new NIST standards

Allows secure transition: RSA / ECC → Hybrid → Pure PQC without silicon respins.

Over-the-Air (OTA) Modernization

Secure devices deployed today must remain secure tomorrow. PQSecure™ enables post-deployment upgrades.

- OTA firmware updates enabling PQC activation

- Remote algorithm replacement

- Secure key rollover mechanisms

- Algorithm deprecation workflows

Critical for: Defense systems, Automotive ECUs, and IoT with long field lifetimes.

Supported Architectures

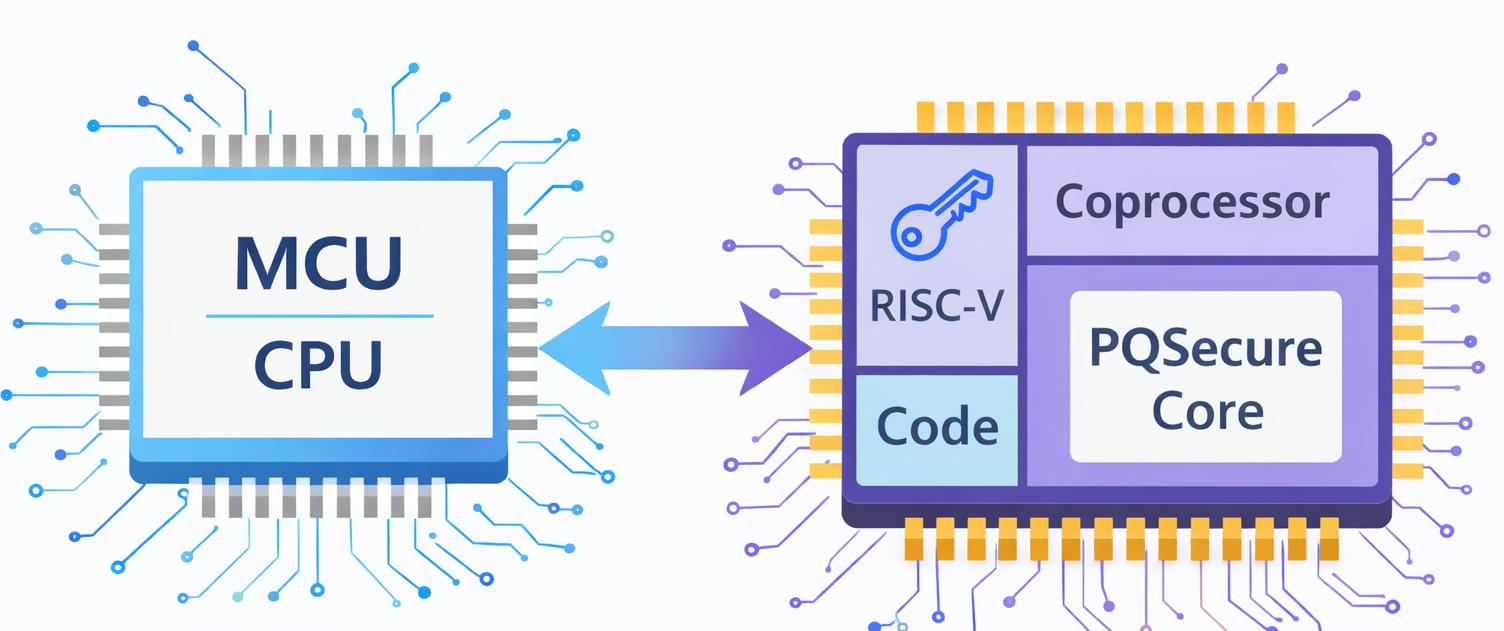

RISC-V Based Architectures

- Hardware PQC accelerators attached via AXI/APB

- Secure Boot ROM integration

- Custom cryptographic instruction extensions (optional)

- Lightweight MCU → Secure SoC scaling

- Root-of-Trust implementations

Ideal for: Secure enclaves, Sovereign silicon programs, Next-generation defense microelectronics.

ARM-Based Architectures

- Cortex-M secure firmware acceleration

- Cortex-A high-performance deployments

- TrustZone-aware architectures

- Secure boot and secure world integration

- Hardware-backed key provisioning

Designed for: Embedded and high-performance systems requiring migration to PQC.

Design Choices

Secure Root-of-Trust Architecture

Typical PQSecure™ co-design architecture combines hardware performance with software flexibility.

(Tiny / Compact / Balanced / High-Performance Tier)

Complete PQC Coverage

Co-Designed Implementations

ML-KEM (FIPS 203)

ML-DSA (FIPS 204)

SLH-DSA (FIPS 205)

FN-DSA (FIPS 206)

XMSS

LMS

Hybrid Classical + PQC

Flexible acceleration paths

Secure software fallback

Gradual migration strategies

Security & Assurance

Hardware Security

- Side-channel-hardened accelerators

- Masking & leakage protections

- Fault injection mitigation

Software Security

- Formally verified C & Rust implementations

- Constant-time enforcement

- Secure update workflows

Independent Evaluation

- Third-party security testing

- Keysight DPA/CPA assessment

- Robustness under adversarial conditions

Why PQSecure-HW/SW Co-Design™

PQSecure™ delivers more than cryptographic IP — we deliver secure migration-ready architectures.

- Crypto Agility engineered at design time

- OTA-ready cryptographic modernization

- RISC-V & ARM ecosystem integration

- Complete PQC algorithm coverage

- Side-channel protected hardware

- Formally verified software

Ensuring today’s silicon remains secure in tomorrow’s quantum world.