Semiconductors

Providing the high-performance building blocks for quantum-ready silicon.

As NIST finalizes FIPS standards, the demand for Post-Quantum Cryptography (PQC) is moving upstream. Chip designers and foundries must now integrate PQC IP into their core architectures to remain competitive. PQSecure provides synthesis-ready RTL and highly optimized IP cores that allow semiconductor companies to deliver quantum resistance without sacrificing precious silicon area or power-efficiency.

The Silicon Area & Power Paradox

Integrating PQC into standard SoC workflows isn’t just about security—it’s about balance. Designers face the “PQC Overhead” where increased key sizes and modular arithmetic can balloon the gate count and stall production.

Foundries and Fabless companies must solve for:

- Gate Count Efficiency: Minimizing the Area (kGate) impact of ML-KEM/ML-DSA accelerators.

- Timing Closure: Achieving high-frequency operation without violating strict timing constraints.

- Physical Resilience: Defending against Side-Channel Attacks (SCA) and Fault Injection (FI) at the gate level.

- Ecosystem Compatibility: Ensuring IP easily integrates via standard AXI/APB bus interfaces.

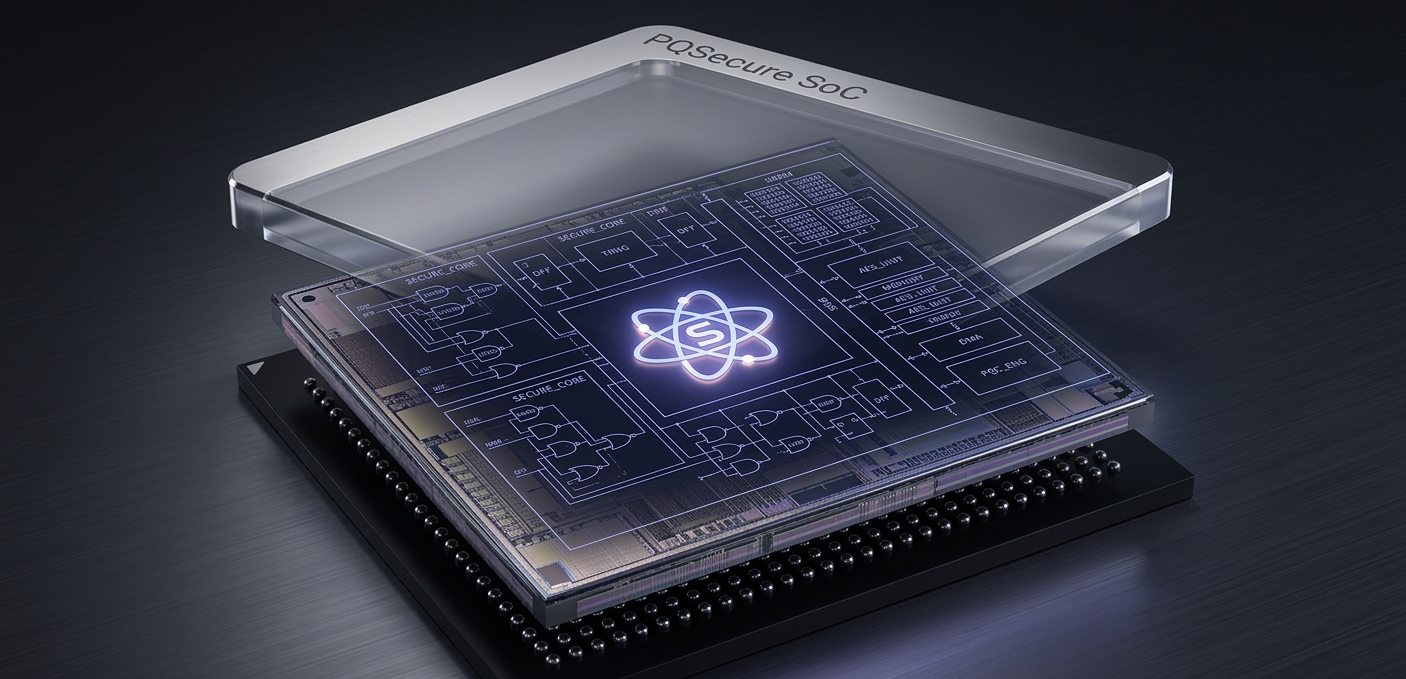

Proven Silicon IP Partner

PQSecure delivers synthesis-ready hardware IP and firmware stacks designed for immediate integration. Our solutions are used by industry leaders in Aerospace, Defense, and Automotive sectors to secure the “Root of Trust” in modern microelectronics.

From Lab to Fab: Standards-compliant security at scale.

Quantum-Ready Building Blocks

We provide the full spectrum of IP cores and software to ensure your next tape-out is quantum-safe.

PQSecure-SW™

Reference Firmware & Models. Highly optimized C and Rust implementations that provide the reference models for hardware verification. Ideal for foundries providing full-stack security reference designs to their customers.

PQSecure-HW™

Synthesis-Ready RTL Cores. Hardware accelerators for ML-KEM and ML-DSA, optimized for Area (Tiny/Compact) or Performance (High-Throughput). Features side-channel hardening and easy integration into standard SoC flows.

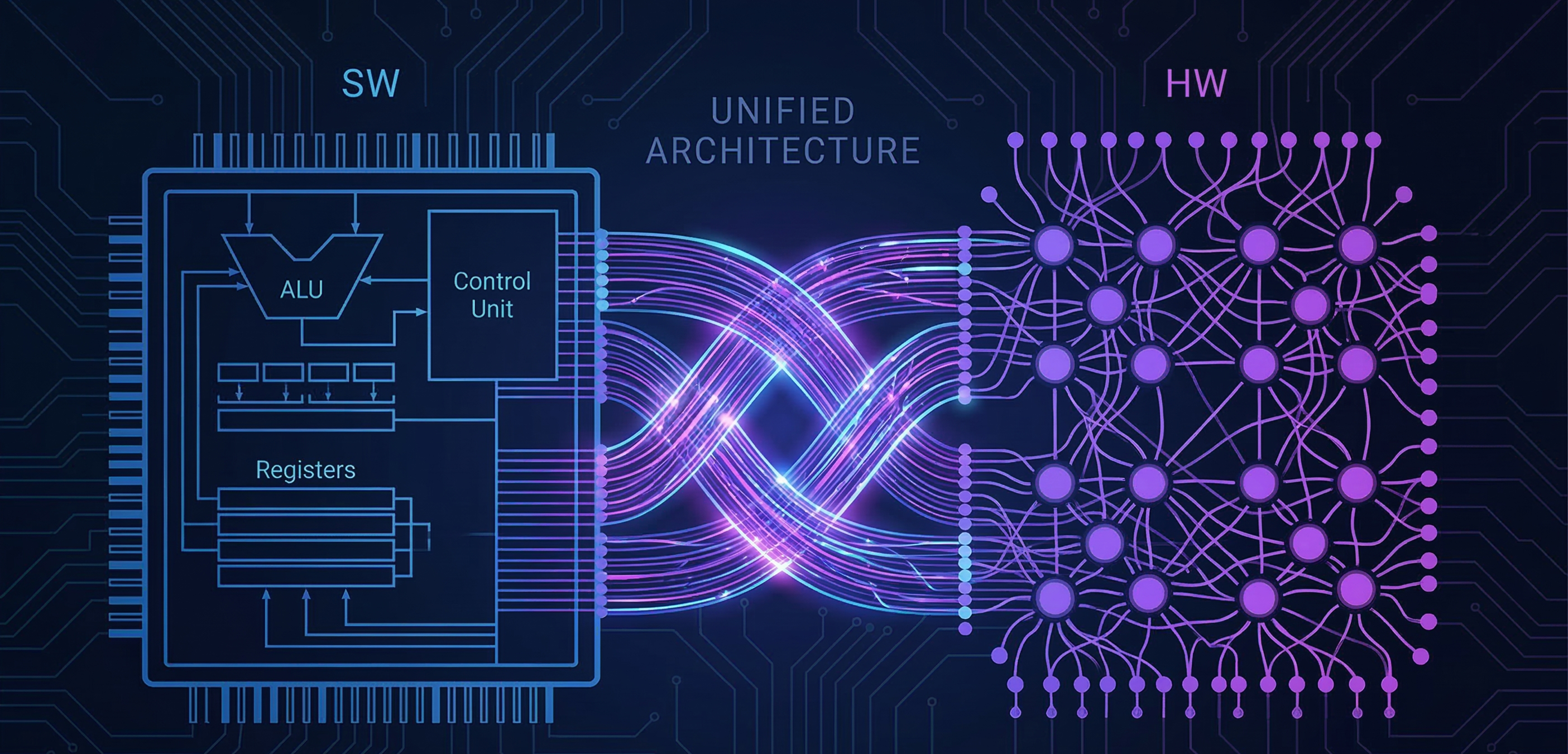

HW/SW Co-Design™

Unified Security Architecture. Tight integration of hardware acceleration with software-defined crypto-agility. Perfect for long-lifecycle silicon where the ability to update algorithms post-deployment is a critical requirement.